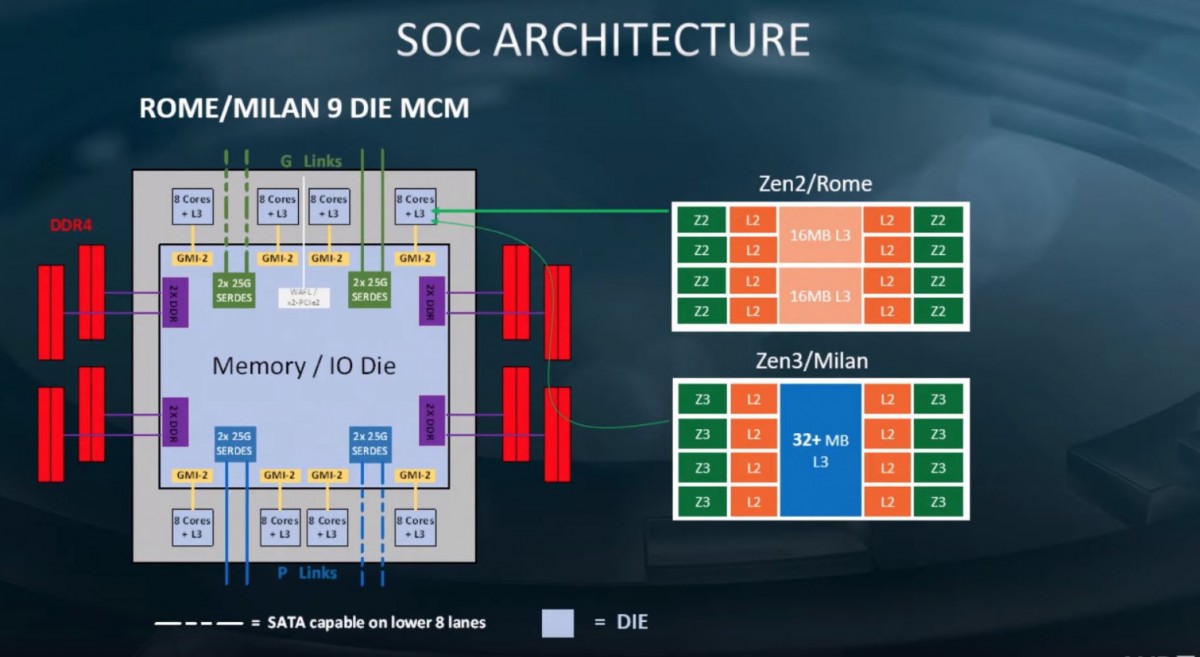

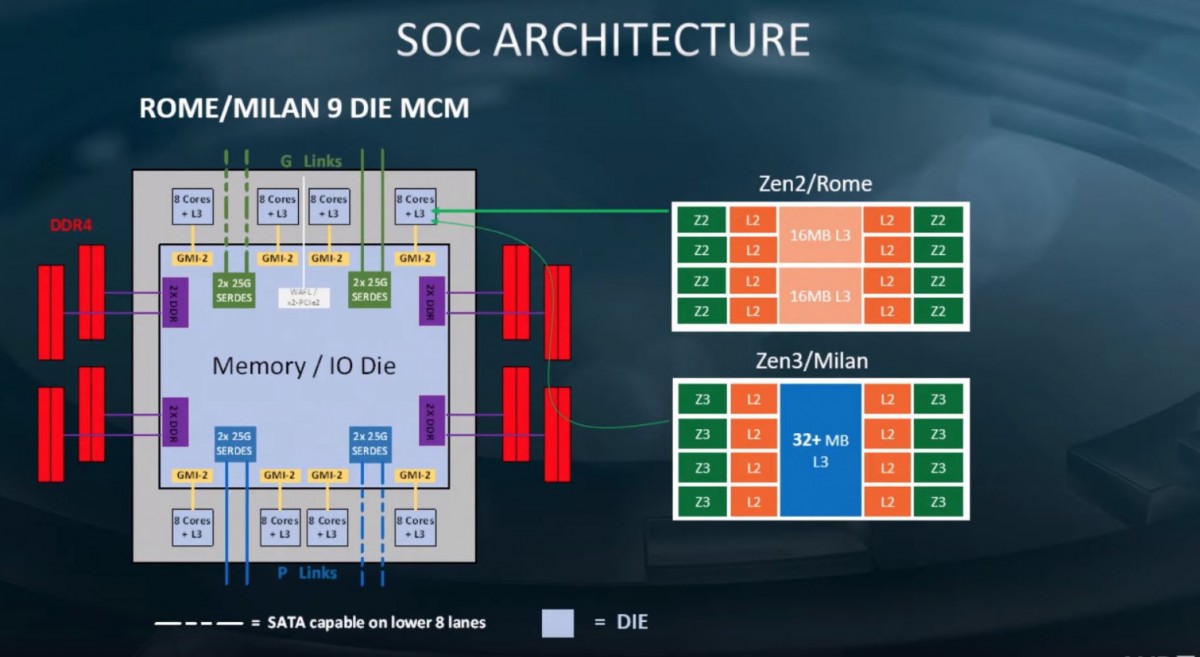

Pour la prochaine gÈnÈration de processeurs en ZEN 3, AMD nous proposera quelques nouvelles Èvolutions et quelques changements. La premiËre sera le passage au 7 nm+ qui permettra de gagner en consommation, en vitesse et surement en OC pour les processeurs de type RYZEN. Mais AMD ne va pas s'arrÍter ‡ cela. En effet, les rouges vont apporter un trËs gros changement au niveau de la gestion du cache L3 dans les CCD. Pour rappel, un CCD est un chiplet qui embarque deux CCX, un CCX Ètant un ensemble de 4 cores avec mÈmoire cache L1, L2 et L3. Les deux CCX, formant le CCD communiquent ensemble via l'Infinity Fabric. Franchement, nous ne sommes pas loin de la grammaire avec les COD, COI, etc etc et cela ne semble pas plus simple ‡ comprendre.

Heureusement, avec un petit tour au CDI de la Ferme, il est facile de comprendre tout cela. Et donc, le gros changement ‡ venir sur les processeurs ZEN 3 est l'unification du cache L3 entre deux CCX. Ainsi, nous n'aurons plus qu'un seul bloc de 32 Mo contre deux blocs de 16 Mo actuellement. LíintÈrÍt est facile ‡ comprendre, il n'y aura plus besoin de communication entre les deux blocs et en plus les deux blocs feront le lien avec les CCX et les diffÈrents cores prÈsents dans ces derniers. Donc nous aurons un gain sur la latence et donc un gain en performance.

Par contre, nous apprenons aussi que les ZEN 3 ne devraient proposer une nouvelle version du SMT et ils resteront donc en 1 Cores = 2 Threads.

Heureusement, avec un petit tour au CDI de la Ferme, il est facile de comprendre tout cela. Et donc, le gros changement ‡ venir sur les processeurs ZEN 3 est l'unification du cache L3 entre deux CCX. Ainsi, nous n'aurons plus qu'un seul bloc de 32 Mo contre deux blocs de 16 Mo actuellement. LíintÈrÍt est facile ‡ comprendre, il n'y aura plus besoin de communication entre les deux blocs et en plus les deux blocs feront le lien avec les CCX et les diffÈrents cores prÈsents dans ces derniers. Donc nous aurons un gain sur la latence et donc un gain en performance.

Par contre, nous apprenons aussi que les ZEN 3 ne devraient proposer une nouvelle version du SMT et ils resteront donc en 1 Cores = 2 Threads.

source : TPU

Marque : AMD

Partagez :

PostÈ le 08 October 2019 ‡ 08:56 par AurÈlien Lagny