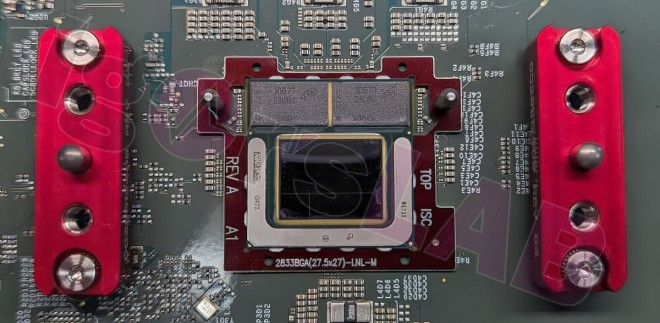

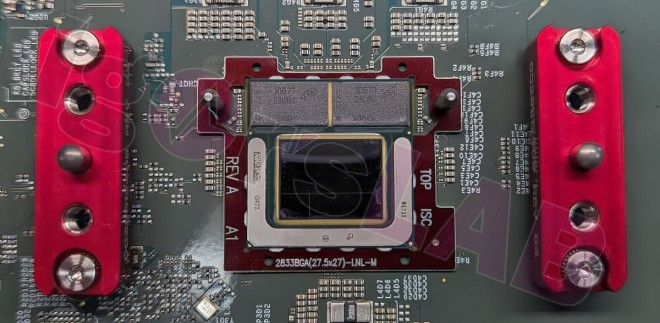

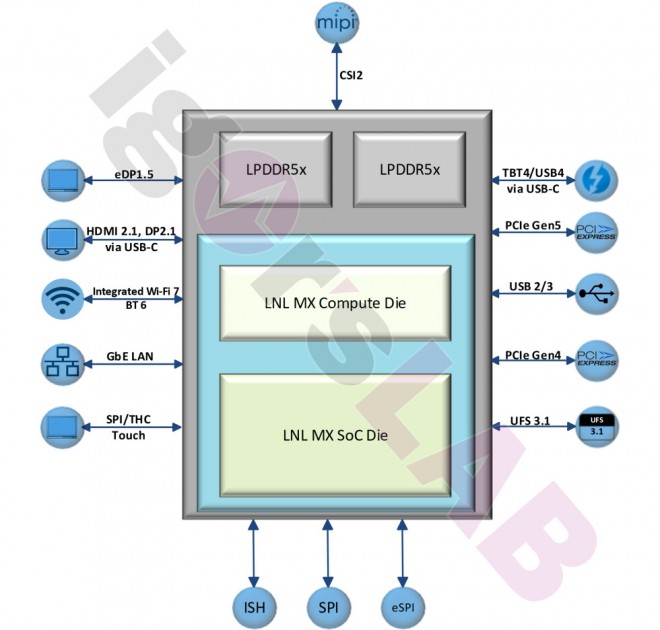

Les processeurs Core Ultra Lunar Lake-MX, seront la réponse d'Intel aux puces Pro et Max de la série M d'Apple, conçue pour alimenter la nouvelle génération d'ultraportables haute performance. L'extension de nom de code MX signifie MoP (memory on package), ce qui permet de superposer des puces de mémoire LPDDR5X sur le substrat, pour réduire l'empreinte sur le circuit imprimé, mais aussi obtenir un meilleur contrôle sur le type de vitesse de mémoire, les timings et les caractéristiques de gestion de l'énergie. Igor's Lab dévoile ce jour pas mal d'informations sur Lunar lake et présente męme des images de Lunar Lake-MX.

Par rapport ŕ Meteor Lake, Lunar Lake propose une réorganisation et une simplification des divers composants du processeur. Sur Meteor Lake, les cśurs du CPU et l'iGPU étaient sur des tuiles séparées, le tout fonctionnant avec une tuile SoC, mais aussi une tuile I/O. L'ensemble prend place sur un interposeur Foveros facilitant l'intégration et le câblage des différents composants entre eux.

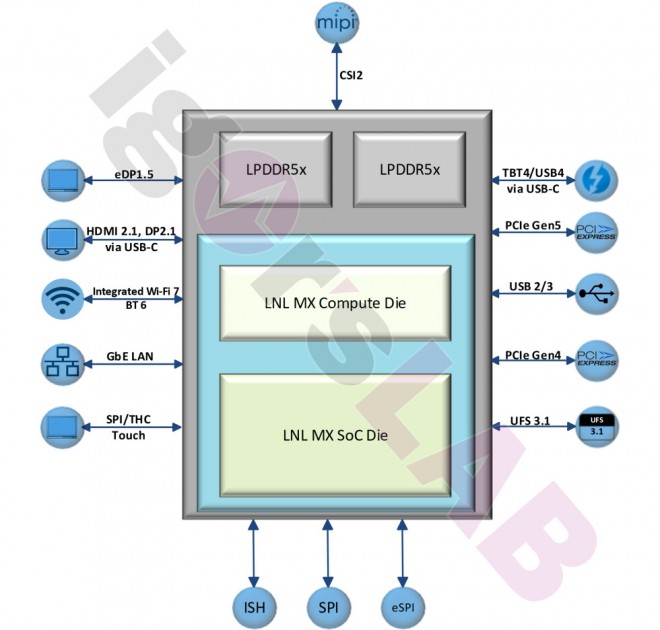

Avec Lunar Lake, on passerait ŕ seulement deux tuiles, ŕ savoir la tuile de calcul et la tuile SoC. La tuile de calcul contient les cśurs du CPU et est construite sur le nśud de fonderie TSMC N3B. C'est un nśud EUV de 3 nm, et il est dit plus avancé que le nśud Intel 4 que la société utilisait pour la tuile de calcul de Meteor Lake. Le processeur présenté par Igor propose une configuration CPU 4P+4E. Cela signifie quatre cśurs P Lion Cove et quatre cśurs E Skymont. l'iGPU de Lunar Lake se trouverait ainsi dans la tuile SoC avec le NPU. iGPU qui devrait ętre en architecture graphique Xe2-LPG Battlemage avec 8 Xe Cores, 64 EU et donc 1024 SP au max.

Passons maintenant aux interfaces disponibles. Nous avons d'abord la mémoire LPDDR5X-8533 sur le package. Le package émet ŕ la fois des lignes PCI-Express Gen 5 et Gen 4. Les lignes Gen 5 sont idéalement destinées ŕ l'interface PEG du chip, ŕ un GPU discret, et ŕ un SSD NVMe Gen 5 ; tandis que les lignes Gen 4 sont destinées pour des SSD NVMe secondaires, ou d'autres dispositifs discrets embarqués. Le processeur intčgre un contrôleur WLAN Wi-Fi 7 + Bluetooth 6, et des MAC pour des contrôleurs GbE filaires. Nous avons aussi du Thunderbolt 4 intégré, et l'interface USB4. Le chip offre également une connectivité USB 3.2 et USB 2.0. Pour l'affichage nous aurions du DisplayPort 2.1, du HDMI 2.1, et du eDP 1.5.

Par rapport ŕ Meteor Lake, Lunar Lake propose une réorganisation et une simplification des divers composants du processeur. Sur Meteor Lake, les cśurs du CPU et l'iGPU étaient sur des tuiles séparées, le tout fonctionnant avec une tuile SoC, mais aussi une tuile I/O. L'ensemble prend place sur un interposeur Foveros facilitant l'intégration et le câblage des différents composants entre eux.

Avec Lunar Lake, on passerait ŕ seulement deux tuiles, ŕ savoir la tuile de calcul et la tuile SoC. La tuile de calcul contient les cśurs du CPU et est construite sur le nśud de fonderie TSMC N3B. C'est un nśud EUV de 3 nm, et il est dit plus avancé que le nśud Intel 4 que la société utilisait pour la tuile de calcul de Meteor Lake. Le processeur présenté par Igor propose une configuration CPU 4P+4E. Cela signifie quatre cśurs P Lion Cove et quatre cśurs E Skymont. l'iGPU de Lunar Lake se trouverait ainsi dans la tuile SoC avec le NPU. iGPU qui devrait ętre en architecture graphique Xe2-LPG Battlemage avec 8 Xe Cores, 64 EU et donc 1024 SP au max.

Passons maintenant aux interfaces disponibles. Nous avons d'abord la mémoire LPDDR5X-8533 sur le package. Le package émet ŕ la fois des lignes PCI-Express Gen 5 et Gen 4. Les lignes Gen 5 sont idéalement destinées ŕ l'interface PEG du chip, ŕ un GPU discret, et ŕ un SSD NVMe Gen 5 ; tandis que les lignes Gen 4 sont destinées pour des SSD NVMe secondaires, ou d'autres dispositifs discrets embarqués. Le processeur intčgre un contrôleur WLAN Wi-Fi 7 + Bluetooth 6, et des MAC pour des contrôleurs GbE filaires. Nous avons aussi du Thunderbolt 4 intégré, et l'interface USB4. Le chip offre également une connectivité USB 3.2 et USB 2.0. Pour l'affichage nous aurions du DisplayPort 2.1, du HDMI 2.1, et du eDP 1.5.

source : Igorlabs

Marque : Intel

Partagez :

Posté le 28 Mars 2024 ŕ 07:56 par Aurélien Lagny