Il y a quelques jours, nous vous annoncions que ZEN 5 pourrait ętre 40 % plus performant que ZEN 4 et ce jour, nous avons peut-ętre l'explication du comment.

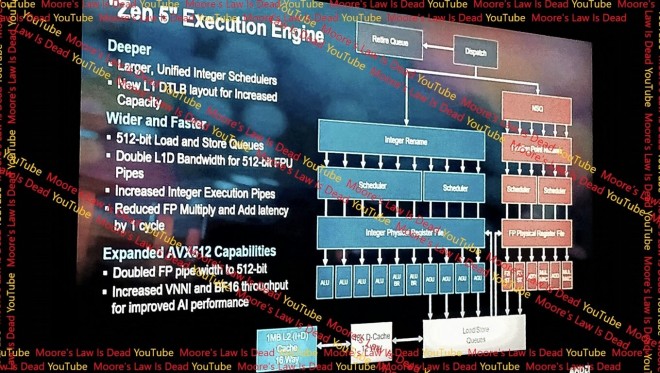

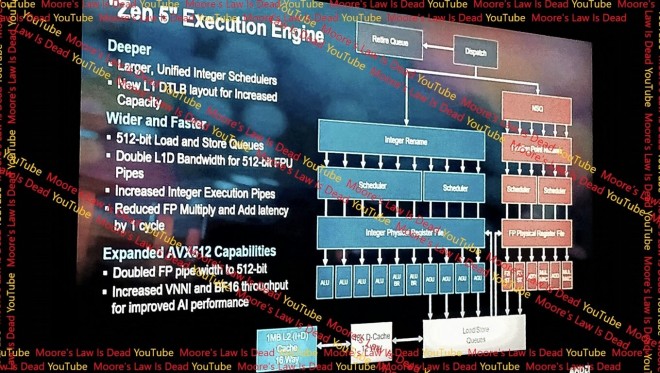

Ce gain de 40 % avec la nouvelle architecture des CPU AMD ZEN 5 se ferait principalement sur les charges de travail AVX-512. Et selon une slide AMD qui a fuité, le moteur d'exécution de ZEN 5 exploite maintenant un vrai FPU 512 bits. Actuellement, avec les processeurs ZEN 4, AMD utilise un double FPU 256 bits pour exécuter les charges de travail AVX-512. Le FPU mis ŕ jour devrait améliorer considérablement les performances en tirant pleinement parti des instructions.

L'intégration d'un FPU 512 bits implique aussi des changements majeurs afin d'augmenter les capacités des composants annexes et de tous les éléments qui alimentent le FPU en données et instructions. Les rouges ont donc augmenté la capacité du L1 DTLB. Les files d'attente de chargement et d'enregistrement ont été élargies pour répondre aux besoins du nouveau FPU. La bande passante du cache de données L1 a été doublée et sa taille a été augmentée de 50%. Le L1D fait désormais 48 Ko, contre 32 Ko pour le CPU ZEN 4. La latence du FPU MADD a également été réduite d'un cycle. Outre le FPU, AMD a également augmenté le nombre d'Execution Pipes ŕ 10, contre 8 sur ZEN 4. Le cache L2 est lui inchangé sur ZEN 5.

C'est assez techniques de bon matin.

Ce gain de 40 % avec la nouvelle architecture des CPU AMD ZEN 5 se ferait principalement sur les charges de travail AVX-512. Et selon une slide AMD qui a fuité, le moteur d'exécution de ZEN 5 exploite maintenant un vrai FPU 512 bits. Actuellement, avec les processeurs ZEN 4, AMD utilise un double FPU 256 bits pour exécuter les charges de travail AVX-512. Le FPU mis ŕ jour devrait améliorer considérablement les performances en tirant pleinement parti des instructions.

L'intégration d'un FPU 512 bits implique aussi des changements majeurs afin d'augmenter les capacités des composants annexes et de tous les éléments qui alimentent le FPU en données et instructions. Les rouges ont donc augmenté la capacité du L1 DTLB. Les files d'attente de chargement et d'enregistrement ont été élargies pour répondre aux besoins du nouveau FPU. La bande passante du cache de données L1 a été doublée et sa taille a été augmentée de 50%. Le L1D fait désormais 48 Ko, contre 32 Ko pour le CPU ZEN 4. La latence du FPU MADD a également été réduite d'un cycle. Outre le FPU, AMD a également augmenté le nombre d'Execution Pipes ŕ 10, contre 8 sur ZEN 4. Le cache L2 est lui inchangé sur ZEN 5.

C'est assez techniques de bon matin.

source : TPU

Marque : AMD

Partagez :

Posté le 05 Avril 2024 ŕ 09:11 par Aurélien Lagny